共源共栅(cascode)结构详解芯片解密

芯片解密安森美 (onsemi) cascode FET (碳化硅共源共栅场效应晶体管)在硬开关和软开关应用中有诸多优势,本文将重点介绍Cascode结构。

Cascode简介

碳化硅结型场效应晶体管(SiC JFET)相比其他竞争技术具有一些显著的优势,特别是在给定芯片面积下的低导通电阻(称为RDS.A)。为了实现最低的RDS.A,需要权衡的一点是其常开特性,这意味着如果没有栅源电压,或者JFET的栅极处于悬空状态,那么JFET将完全导通。

然而,开关模式在应用中通常需要常关状态。因此,将SiC JFET与低电压硅MOSFET以cascode 配置结合在一起,构造出一个常关开关模式“FET”,这种结构保留了大部分SiC JFET的优点。

Cascode结构

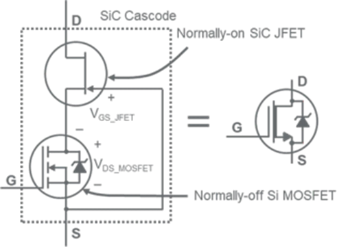

共源共栅(Cascode)结构是通过将一个SiC JFET与一个低压、常关的硅(Si)MOSFET串联而成,其中JFET的栅极连接到MOSFET的源极。MOSFET的漏源电压是JFET栅源电压的反相,芯片解密从而使cascode 结构具有常见的常关特性。该结构可在额定漏源电压范围内阻断电流,但如同任何MOSFET(无论是硅基还是碳化硅基器件)一样,其反向电流始终可以流通。

图 1 Cascode配置

当内部MOSFET导通或有反向电流流过时,不论cascode的栅极电压如何,JFET的栅极-源极电压几乎为零,JFET处于导通状态。当MOSFET关断且cascode两端存在正的VDS(漏源电压)时,MOSFET的VDS会增加,与此同时JFET的栅源电压会降低至低于JFET的阈值电压,从而关断 JFET。请参见图1。

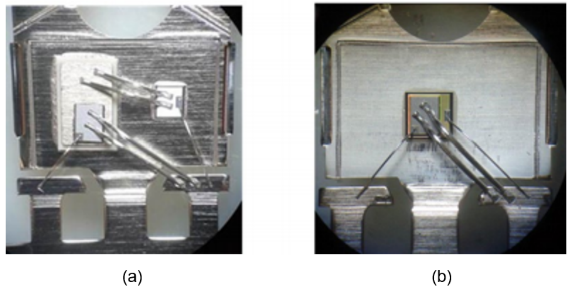

图 2 分立cascode结构

分立cascode 结构采用并排芯片,如图 2(a)所示,或堆叠芯片,如图 2(b)所示。在这两种情况下,SiC JFET 通常都是银烧结在封装引线框架上。

在并排配置中,MOSFET 安装在一个金属镀层的陶瓷隔离器上,芯片解密有两组源极连接线:一组连接 JFET 源极和 MOSFET 漏极(金属镀层陶瓷的顶面),另一组连接 MOSFET 源极和源极引脚。在堆叠芯片配置中,JFET 源极和 MOSFET 漏极之间的连接线被取消,从而减少了杂散电感。并采用直径较小的连接线连接 JFET 和 MOSFET 栅极。

芯片解密

芯片解密